# Microwave Inductors and Capacitors in Standard Multilevel Interconnect Silicon Technology

Joachim N. Burghartz, *Senior Member, IEEE*, Mehmet Soyuer, *Member, IEEE*, and Keith A. Jenkins

**Abstract**—Spiral inductors and metal-to-metal capacitors for microwave applications, which are integrated on a silicon substrate by using standard  $0.8 \mu\text{m}$  BiCMOS technology, are described. Optimization of the inductors has been achieved by tailoring the vertical and lateral dimensions and by shunting several interconnect metal layers together. Lumped element models of inductors and capacitors provide detailed understanding of the important geometry and technological parameters on the device characteristics. The high quality factors of nearly 10 for the inductors are among the best results in silicon, particularly when using standard silicon technology.

## I. INTRODUCTION

**M**ONOLITHIC MICROWAVE integrated circuits (MMIC's) are rapidly outpacing discretes in mobile wireless communication products [1]. The maturity, high integration level, and low-cost aspects of silicon technology make particularly Si-BiCMOS a serious contender for this high-volume market. Besides its superiority at intermediate frequencies (IF), the advent of SiGe-HBT's in submicrometer, self-aligned structures allows silicon technology to cope well with GaAs at microwave and millimeterwave frequencies [2], [3]. The major concern about the use of silicon are the high substrate losses due to the much lower substrate resistivity compared to GaAs. Also, aluminum-copper (AlCu) interconnects are typically used, which have a higher resistivity than the gold (Au) metalization used in GaAs technology, and the metal thickness is also smaller than in GaAs. Transmission line fabrication and the design of high-Q inductors and capacitors are therefore difficult tasks in standard silicon technology. Although substrate losses can be considerably reduced by using high-resistivity (HRS) or silicon-on-insulator (SOI) substrates [4], the results and discussions in this paper will show that high-Q inductor and capacitor designs are possible even in standard silicon technology.

In Section II, the fabrication process of the experimental inductors and capacitors is described, and in Section III the measurement results are summarized, models for inductors and capacitors are presented, and the parameter impacts are discussed. Section IV gives conclusions and provides an outlook on possible future developments and trends.

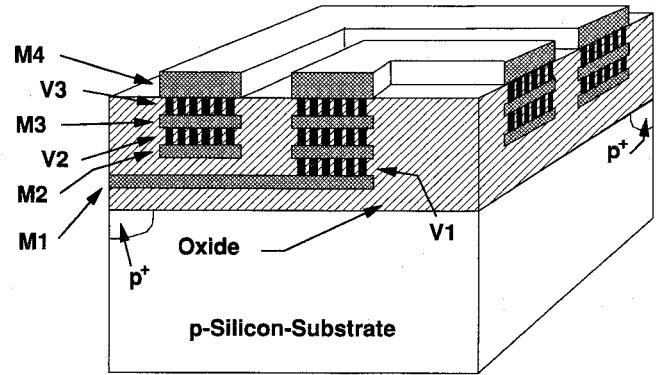

Fig. 1. Cross-sectional view of the four level interconnect scheme provided with the  $0.8 \mu\text{m}$  BiCMOS technology which was used. The center section of a spiral inductor structure is shown. (Note that the silicon region under the inductor was protected from any additional implant.)

## II. INDUCTOR AND CAPACITOR FABRICATION PROCESS

A  $0.8 \mu\text{m}$  BiCMOS technology with four levels of AlCu interconnects was used to fabricate various inductor and capacitor structures [5]. A cross section of the center part of a spiral inductor structure, involving all metal levels, is shown in Fig. 1. The thickness of the first (M1), second (M2), and third (M3) metal layer was about  $1.0 \mu\text{m}$ , while the fourth (M4) metal layer was about  $2.0 \mu\text{m}$  thick. The isolating oxide between metal layers was  $1.5 \mu\text{m}$  thick, and the oxide thickness between M2 and the silicon substrate was about  $4.5 \mu\text{m}$ . M2 was the lowest metal level used in the inductor and capacitor structures, except for the inductor's underpass which was at M1. The substrate resistivity under the inductors was  $10 \text{ ohm}\cdot\text{cm}$  in most cases, but one inductor structure was also fabricated over a p-well region with a resistivity of  $\sim 0.1 \Omega\cdot\text{cm}$  at  $\sim 1.1 \mu\text{m}$  well depth. The p-well was also present under the metal-insulator-metal (MIM) capacitors.

In GaAs MMIC technology, interdigital capacitors are most commonly used because they require only one metal level and provide the small capacitance values required for microwave/millimeter wave applications [6]. Much larger capacitance values are needed in silicon VLSI technology because circuits operate at MHz frequencies. The preferred structure here is the MOS-capacitor which has a high capacitance/area ratio. The MOS-cap, however, has one silicon contact electrode, and therefore the achievable Q is relatively small. Both device structure concepts are not very well suited for L-band and S-band applications, due to a large area consumption as far as the interdigital capacitor goes, and poor parameter control

Manuscript received April 9, 1995; revised October 2, 1995.

The authors are with IBM Research Division, T. J. Watson Research Center, Yorktown Heights, NY, 10598, USA.

Publisher Item Identifier S 0018-9480(96)00473-5.

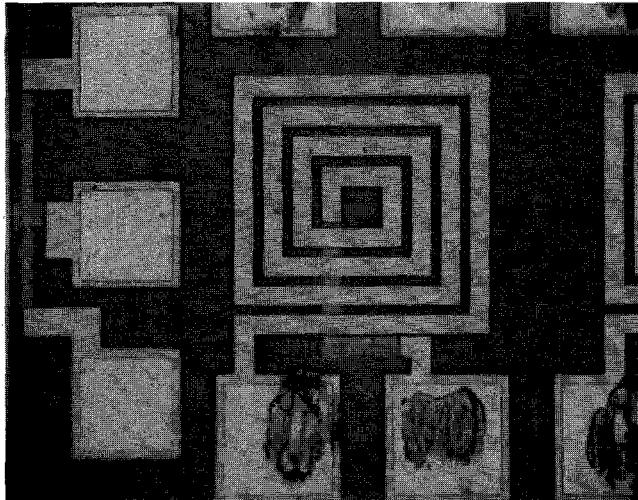

Fig. 2. Plan view photograph of the inductor M2/M3/M4 on the chip.

at small geometries and low Q's for the MOS-cap. A better solution at these frequencies is the MIM capacitor which has advantages due to the moderate capacitance/area values and high Q-factors with the two metal contacts. For this work we fabricated dual MIM-capacitors with use of the M1, M2, and M3 metal levels. For the S-parameter measurements, M2 and M3 were contacted and M1 was left floating. But it is also possible to connect M1 and M3 to form one contact and use M2 as the second contact of the dual capacitor in order to double the capacitance per area.

Inductor fabrication on a chip is typically achieved by the formation of a spiral with a square, beveled, or round footprint and with a metal underpass [7]. Thus an interconnect technology with at least two metal levels is required. Multilevel interconnects are a common feature of todays silicon VLSI technologies, but the processes developed to achieve a metal pitch of the order of a few micrometers leads to a limitation in metal thickness. This limitation results from the fact that the metal lines are dry-etched to generate micrometer-size pattern, and not structured by lift-off or similar techniques used to fabricate coarser geometries [8]. Effectively thicker metal wires can be realized in standard silicon technology by connecting multiple metal layers with dense via arrays. In this work, inductors with one (M3), two (M2/M3 or M3/M4), and three (M2/M3/M4) metal levels were built to explore this design option and to achieve high Q-factors (Table I). In all cases the underpass was at M1 to ensure that the spacing between inductor and the substrate was maximum and thus substrate losses were minimum. The importance of this design aspect will be explained in Section III. The lateral dimensions of the inductors were the same, with four turns, an inductor area (footprint) of  $226 \times 226 \mu\text{m}^2$ , and  $16 \mu\text{m}$  metal width and  $10 \mu\text{m}$  metal-metal space (i.e.,  $26 \mu\text{m}$  metal pitch). A plan view photograph of the M2/M3/M4-inductor is shown in Fig. 2.

Inductor and capacitor structures were connected to high-frequency test pads for S-parameter analysis. The metal pads had the full pad size at the M4 level, but the via arrays and lower metal layers were limited in size to minimize the

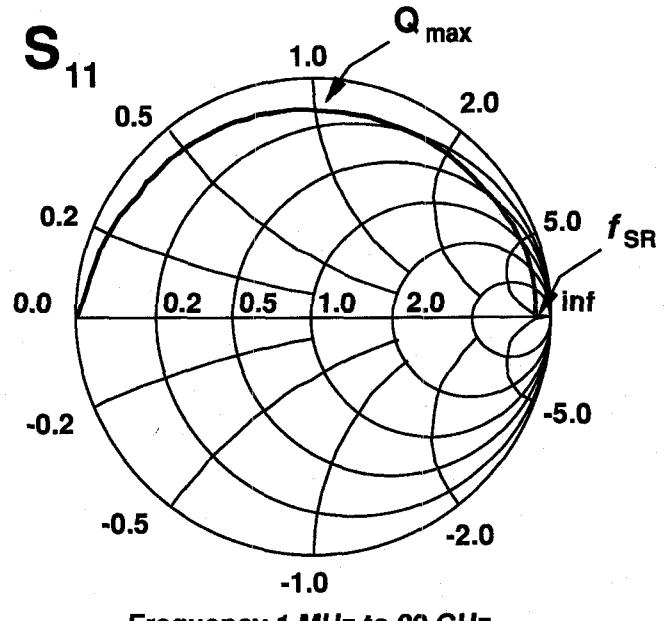

Fig. 3. Smith chart measurement results of inductor M2/M3/M4. The markers indicate the frequency of  $Q_{\max}$  and the self-resonance frequency.

metal to substrate capacitance. Open-contact, short, and  $50 \Omega$  calibration structures were placed in close proximity to the individual sites for proper elimination of parasitics prior to the S-parameter analyses.

### III. RESULTS AND DISCUSSION

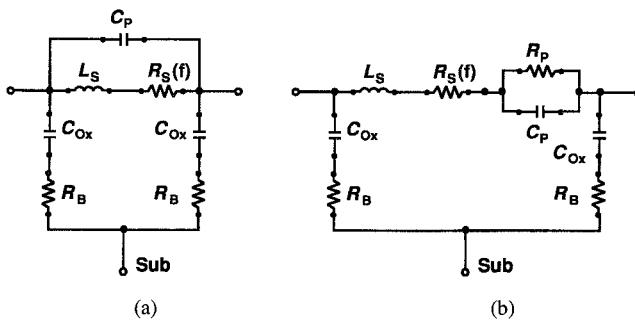

The experimental devices were characterized by using a 20 GHz HP8720B network analyzer and on-wafer measurements with microwave probes. The parasitic capacitances and the contact resistance were accurately subtracted from the measurement data with calibrations on the open, short, and  $50 \Omega$  resistor sites. The  $S_{11}$  parameter was extracted from a one-port measurement of the reflection coefficient. A smith chart of the M2/M3/M4 inductor measurement is shown in Fig. 3. The markers in this figure indicate the frequencies of maximum Q and the self-resonance frequency. The impedances  $Z_{in}$  were then derived from  $S_{11}$  versus frequency data for all inductors and the MIM capacitor. The inductor data were compared with the model in Fig. 4(a), which is similar to the one published in [9]. The capacitances  $C_P$  and  $C_{OX}$  were calculated by using an electromagnetic simulation (EMS) tool [10]. The values for the inductance  $L_S$  were also derived from EMS, and had only little frequency dependence until frequencies approached self-resonance. The series resistance of the inductor spiral,  $R_S$ , was determined by EMS only for the single-layer M3-inductor. For the other structures with the very complex via arrays the number of mesh elements became too large to solve the problem in an acceptable time frame. Therefore, worst and best cases of metal thickness were calculated with EMS, and  $R_B$  was used as a fitting parameter within that data window at a given frequency. The frequency dependence of  $R_S$  due to the skin effect was considered in the model [11], [12]. The values of  $R_B$  depend on the resistivity of the silicon substrate under the inductor and on the lateral dimensions. Its order

Fig. 4. Lumped element equivalent circuits for the integrated inductor (a) and MIM capacitor, (b) structures.

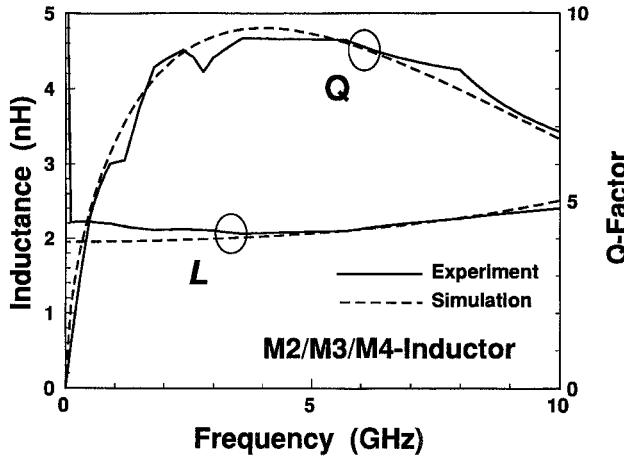

Fig. 5. Inductance and  $Q$ -factor of inductor M2/M3/M4 as a function of frequency.

of magnitude was estimated, but in the comparison with the data,  $R_B$  was used as a fitting parameter as well. The MIM capacitor model in Fig. 4 includes the device capacitance  $C_P$ , the series resistance  $R_S$ , the resistance  $R_P$  which describes the dielectric losses, the lead inductance  $L_S$ , and the substrate elements  $R_B$  and  $C_{OX}$  as described above.

The lumped element equivalent circuits in Fig. 4 were compared with the measured data by using the HP-EEspresso Communication Design Suite (CDS) tool [12] for the calculation of the  $S_{11}$  parameters. Excellent agreements between measured data and models were achieved from the practical frequency range up to self-resonance as shown in Fig. 5, which is an important prerequisite for successful circuit design. The lumped element values for the different inductor and the MIM capacitor configurations, as well as the dc resistances of the inductors, are summarized in Table I. A brief summary of the measurement results can also be found in [13].

An initial evaluation of the data showed that the inductances were little dependent on the vertical configuration of the spiral structures. The inductances were also fairly independent of frequency as a result of the high self-resonance frequencies ( $f_{SR}$ ). This was mainly due to the large spacing between the inductor spiral and the lossy substrate, but also a result of the sufficiently high resistivity of the bulk silicon, which gave high  $R_B$  and small  $C_{OX}$  values. Therefore,  $f_{SR}$  was mainly affected by the fringing capacitance  $C_P$  instead of the much larger  $C_{OX}$ .  $C_P$  depends on the metal spacing which was 10

TABLE I

SUMMARY OF MEASUREMENT AND EQUIVALENT CIRCUIT LUMPED ELEMENT DATA FOR THE DIFFERENT INDUCTORS AND THE MIM CAPACITOR FABRICATED

|                    | Spiral Inductors |                |                   |                |            | MIM           |

|--------------------|------------------|----------------|-------------------|----------------|------------|---------------|

|                    | M2/M3<br>coarse  | M2/M3<br>dense | M2/M3/M4<br>dense | M3/M4<br>dense | M3<br>none | M2/M3<br>none |

| $L_s / nH$         | 2.1              | 2.1            | 1.95              | 2.0            | 2.15       | 0.04          |

| $R_s / \Omega$     | 4.3              | 4.2            | 3.2               | 3.5            | 5.2        | 0.35          |

| $C_P / pF$         | 0.037            | 0.035          | 0.03              | 0.035          | 0.03       | 2.15          |

| $C_{OX} / pF$      | 0.18             | 0.18           | 0.18              | 0.12           | 0.18       | 0.39          |

| $R_B / \Omega$     | 800              | 800            | 900               | 850            | 950        | 20            |

| $R_{dc} / \Omega$  | 3.2              | 2.9            | 2.0               | 2.1            | 5.3        | -             |

| $Q_{max}$          | 7.4              | 7.6            | 9.3               | 8.6            | 6.5        | 80            |

| $f(Q_{max}) / GHz$ | 4                | 4              | 4                 | 4              | 4.7        | 2.5           |

| $f_{SR} / GHz$     | 18               | 18.5           | 20                | 18.5           | 20         | >20           |

$\mu m$  in all cases so that the values of  $C_P$  were small. Therefore,  $f_{SR}$  was much larger than the frequency of practical interest. If  $C_{OX}$  is larger and  $R_B$  is much reduced,  $f_{SR}$  can drop to the low GHz range. The inductance at the operating point then would become strongly dependent on frequency, which would make the device parameters too variable with manufacturing tolerances [7], [14]. The  $Q$ -factor was found to improve with adding additional metal layers through via arrays (M2/M3 versus M2/M3/M4 and M3 versus M3/M4 in Table I). The density of the vias did not have a significant effect on  $Q$ , at least not for the two modifications studied which are the two M2/M3-inductor modifications in Table I. The “coarse” via array covered about 30% of the length of the inductor spiral, for the “dense” via array it was about 45%. The via lengths were 15.6  $\mu m$  and 20  $\mu m$ , respectively.

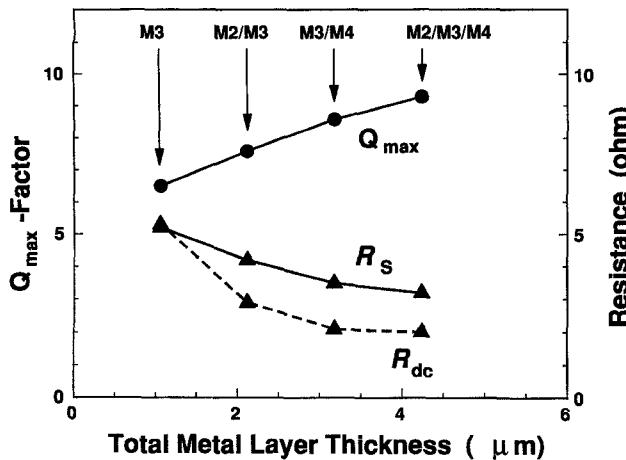

Fig. 6 shows the maximum  $Q$ -values ( $Q_{max}$ ) and the ac and dc resistances of the fabricated inductor modifications in Table I as a function of the total metal thickness. An effective metal layer thickness which could have been attributed to the via arrays was not considered because the comparison of the two M2/M3 inductors did not present any clear evidence of a significant contribution of the vias to the lateral current transport in the inductor structures. A first observation in Fig. 6 was that  $Q_{max}$  did not increase in proportion to the total metal thickness, even without consideration of the lateral current transport through the vias. The same observation was made for the ac and dc resistances which did not decrease linearly with the metal thickness. A qualitative understanding of this result is possible if one considers that in AlCu interconnect technology the tungsten (W) vias have about a three times higher resistivity than AlCu. In addition, the metal layers are typically formed in a sandwiched structure with thin metal films of higher resistivity on top and at the bottom of the AlCu film in order to overcome certain technological problems [15]. For these reasons, the M4 layer, which was

Fig. 6. The  $Q_{\max}$ -factors and ac and dc resistances of the different inductor structures in Table I as function of the total metal layer thickness (not including vias).

not contacted though vias and which has the largest thickness, was conducting a major fraction of the current. This explains why the increase of  $Q_{\max}$  with the total metal thickness was not as strong as one would expect.

In addition, we had fabricated the M2/M3-inductor with and without an increased substrate doping due to the p-well formation mentioned earlier in Section II to evaluate the sensitivity of  $Q$  to the substrate losses. As a result  $Q$  was reduced by nearly 15% at 2.5 GHz for the inductor with the p-well underneath, which highlights the importance of keeping the doping level under the inductor as low as possible.

With solely considering standard silicon technology, the  $Q_{\max}$ -factor of close to 10 with a self-resonance at 20 GHz for the M2/M3/M4 inductor represents one of the best results published to date for monolithically integrated spiral inductors. It should be noted that this result was based on 1-port S-parameter analysis, i.e., with the substrate left floating. With a grounded substrate,  $Q_{\max}$  can be somewhat lower. For an ideally grounded substrate, which is never the case due to the high substrate resistivity,  $Q_{\max}$  would drop from 9.3 to 8.0 for the M2/M3/M4 inductor, based on model extrapolation. But with a resistance of the order of  $R_B$  between substrate contact and inductor, which is a more realistic assumption,  $Q_{\max}$  would be reduced to about 9.0 only. In the published work on integrated inductors, similar results were achieved only by deviating from standard silicon technology. The suppression of the impact of the isolation capacitance  $C_{\text{OX}}$ , in order to keep the self-resonance frequency at high values, had been achieved before either by using micromachining techniques [14] or very high resistive substrates [16]. The inductor resistance had been lowered by using Au interconnects [16] or MCM technology for interconnections [8] which, however, does not allow an integration with submicrometer circuits on the same chip.

For the MIM capacitor a maximum  $Q$  of about 80 was measured, and the self-resonance frequency was higher than 20 GHz. The high  $Q_{\max}$  was clearly a result of the two metal contacts in the MIM structures. For comparison, a MOS-capacitor which was fabricated in the same experiment had a similar capacitance value with a  $Q$  of only 3.

#### IV. CONCLUSION

The important issues to be considered for the microwave design of inductors and capacitors, which are monolithically integrated in silicon, have been highlighted in this work. Optimization based on this understanding has led to inductors with  $Q$ 's approaching 10, which is one of the best results reported to date for silicon integrated inductors. The key design features were a large spacing of the inductor from the lossy silicon substrate and a reduction of the inductor resistance by shunting several layers of metal though via arrays. In spite of the good results achieved, it became clear that an inductor fabricated in a multilayer interconnect technology does not reach the  $Q$ -values possible with an equivalent one-layer structure. The inductor  $Q$  achievable in standard silicon technology seems sufficient for the fabrication of integrated broadband matching networks, but the design of narrow-band filters appears to be difficult. For monolithically integrated passive filters at 2.5 GHz and beyond, a much higher inductor  $Q$  is required. In order to be able to built such inductor structures with  $Q$ 's of 30 or higher it is inevitable to deviate from standard silicon technology. Future developments of silicon MMICs should consider Au or Cu interconnects and HRS substrates or SOI wafers with very thick buried oxide layers.

#### ACKNOWLEDGMENT

The authors would like to thank the IBM Microelectronics Division, Essex Junction, VT, USA, for hardware fabrication. The electromagnetic simulation tool EXCALIBUR, which had been developed by Dr. S. Ponnappalli and others from IBM Research Division, had been used for the verification of some of the inductance values. They would also like to thank Dr. W. Pence and Dr. J. Ewen for their managerial support and their interest in the work.

#### REFERENCES

- [1] R. Schneiderman, "Who's winning the wireless way?" *Microwaves & RF*, pp. 31–36, Oct. 1994.

- [2] J. N. Burghartz, T. O. Sedgwick, D. A. Grützmacher, D. Nguyen-Ngoc, and K. A. Jenkins, "APCVD-grown self-aligned SiGe-base HBTs," in *Proc. Bipolar/BiCMOS Circuits Technol. Meet. (BCTM)*, 1993, pp. 55–62.

- [3] D. L. Harame, J. M. C. Stork, B. S. Meyerson, K. Y.-J. Hsu, J. Cotte, K. A. Jenkins, J. D. Cressler, P. Restle, E. F. Crabbé, S. Subbanna, T. E. Tice, B. W. Scharf, and J. A. Yasaitis, "Optimization of SiGe HBT technology for high speed analog and mixed-signal applications," in *Tech. Dig. Int. Electron Devices Meet. (IEDM)*, 1993, pp. 71–74.

- [4] S. R. Taub and S. A. Alterovitz, "Silicon technologies adjust to RF applications," *Microwaves & RF*, pp. 60–74, Oct. 1994.

- [5] J. Gross, H. Chuang, and T. Schmerbeck, "State-of-the-art analog BiCMOS," in *IEEE GaAs IC Symp.*, Oct. 1993.

- [6] E. Pettenpaul, H. Kapusta, A. Weisgerber, H. Mampe, J. Luginsland, and I. Wolff, "CAD Models of lumped elements on GaAs up to 18 GHz," *IEEE Trans. Microwave Theory Tech.*, vol. 36, no. 2, pp. 294–304, 1988.

- [7] N. M. Nguyen and R. G. Meyer, "Si IC-compatible inductors and LC passive filters," *IEEE J. Solid-State Circuits*, vol. 25, no. 4, pp. 1028–1031, 1990.

- [8] R. G. Arnold and D. J. Pedder, "Microwave characterization of microstrip lines and spiral inductors in MCM-D technology," *IEEE Trans. Comp., Hybrids, and Manufact. Technol.*, vol. 15, no. 6, pp. 1038–1045, 1992.

- [9] D. Lovelace, N. Camillieri, and G. Kannell, "Silicon MMIC inductor modeling for high volume, low cost applications," *Microwave J.*, pp. 60–71, Aug. 1994.

- [10] S. Ponnappalli, A. Deutsch, and R. Bertin, "A package analysis tool based on a method of moments surface formulation," *IEEE Trans. Comp., Hybrids and Manufact. Technol.*, vol. 16, no. 8, pp. 884-892, 1993.

- [11] I. Bahl and P. Bhartia, *Microwave Solid State Circuit Design*. New York: Wiley.

- [12] User manual, Communications Design Suite for RF/Board Design, HP-EEsof, Series IV.

- [13] M. Soyuer, J. N. Burghartz, K. A. Jenkins, S. Ponnappalli, J. F. Ewen, and W. E. Pence, "Multi-level monolithic inductors in silicon technology," *Electron. Lett.*, to be published.

- [14] J. Y.-C. Chang, A. A. Abidi, and M. Gaitan, "Large suspended inductors on silicon and their use in a 2- $\mu$ m CMOS RF amplifier," *IEEE Electron Device Lett.*, vol. 14, no. 5, pp. 246-248, 1993.

- [15] S. Wolf, "Silicon processing for the VLSI era," vol. 2, in *Process Integration*. Sunset Beach, CA: Lattice Press.

- [16] K. B. Ashby, W. C. Finley, J. J. Bastek, and S. Moinian, "High Q inductors for wireless applications in a complementary silicon bipolar process," in *Proc. Bipolar/BiCMOS Circuits and Technol. Meet. (BCTM)*, 1994, pp. 179-182.

**Joachim N. Burghartz** (M'90-SM'92) received the Dipl. Ing. degree from the Technische Hochschule Aachen, Germany, in 1982, and the Ph.D. degree from the University of Stuttgart, Germany, in 1987, both in electrical engineering. From 1982 to 1987 he was with the University of Stuttgart, Germany, where he developed integrated magnetic-field sensors. In 1987 he joined the IBM Thomas J. Watson Research Center working first on selective epitaxial growth for applications in self-aligned silicon bipolar transistors. From 1988 to 1992 he worked on the development of an integrated SiGe bipolar technology with emphasis on doping profile design, SiGe film stability, low-parasitic device integration, and narrow poly-emitter formation. From 1992 to 1993 he was responsible for a part of the development of a 0.15  $\mu$ m CMOS technology at the IBM Hopewell-Junction facility. Since 1993 he is with the Communications and Analog Design Department at the T.J. Watson Research Center with interest in BiCMOS and SiGe bipolar circuit design for analog and mixed signal applications, including the optimization of passive integrated components for silicon microwave circuits.

From 1992 to 1994 Dr. Burghartz served at the IEDM as a subcommittee member and chairman for solid-state devices. He is currently serving as a US corresponding member for ESSDERC and at the BCTM as a subcommittee member for analog design.

**Mehmet Soyuer** (S'79-M'88) was born in Turkey on July 25, 1954. He received the B.S. and M.S. degrees in electrical engineering from the Middle East Technical University, Ankara, Turkey, in 1976 and 1978, and the Ph.D. degree in electrical engineering from the University of California, Berkeley, in 1988.

He joined IBM, T.J. Watson Research Center, Yorktown Heights, NY, as a Research Staff member in 1988. He received several IBM Research Division Awards and authored numerous articles in the area of analog, mixed-signal and nonlinear electronic circuit design. At present, he is the Project Leader for Si and SiGe RF IC designs covering frequency bands from 1 to 6 GHz. His research interests include high-speed integrated circuits, technologies, and subsystems for data communications. He holds two U.S. patents.

**Keith A. Jenkins** received the Ph.D. degree in physics from Columbia University, for work done in experimental high energy physics.

He continued in this field at The Rockefeller University until 1983, when he joined the IBM Research Division at the T.J. Watson Research Center. At IBM, he first worked in Josephson technology. He later joined the Silicon Technology Department, where we worked in a variety of device and circuit subjects, including high frequency measurement techniques, electron beam circuit testing, radiation-device interactions, and low temperature electronics. He is now a member of the VLSI Design and Communication Technology Department. His current activities include research in passive electron-beam inspection techniques, and in transient behavior of silicon-on-insulator (SOI) FET's.